Vhdl Program For 8 Bit Up Down Counter Two

Vhdl Program For 8 Bit Up Down Counter Two Average ratng: 4,2/5 6607 reviews

The suite life on deck movie torrent. VHDL Code for 4-Bit Binary Up Counter January 10, 2018 February 13, 2014 by shahul akthar The clock inputs of all the flip-flops are connected together and are triggered by the input pulses.

This time we'll be designing a 8-bit binary counter using VHDL and then implement it physically on Elbert FPGA Board.

The VHDL Code:

PART A : VHDL Code for 8-bit binary counter and simulation.

The VHDL Code:

Now, we need a VHDL Testbench code to simulate the above VHDL code. The Xilinx ISE generates most-of-the code required for a testbench (Although for larger designs, we need to edit the generated template, or write a new testbench code altogether). The code given below was generated completely by the Xilinx ISE.

Testbench Code:

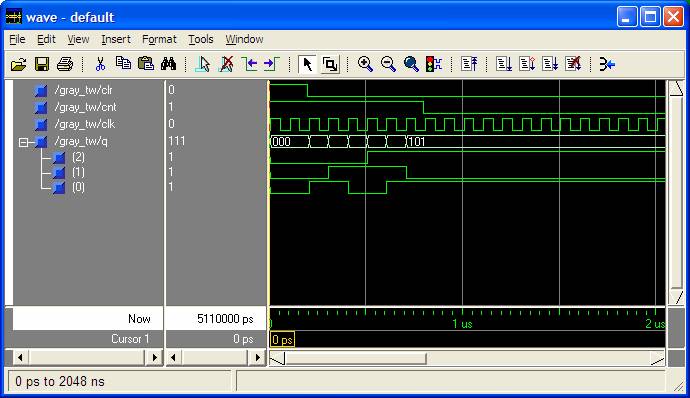

Here is the simulation output of the 8-bit counter VHDL code, using the above testbench code, in Xilinx ISIM simulator.

| Simulation output in Xilinx ISIM for 8-bit binary up counter |

PART B: Implementation on Elbert

Writing and simulating a VHDL code is slightly different from implementing it physically on the FPGA. We have to take care of some things, such as the VHDL code may have some non-synthesizable snippets, take care of FPGA constraints etc.

In case of our 8-bit counter, we need to notice few things:

- The Input clock to Elbert has 12MHz frequency. This is so fast that, if we were to connect the counter outputs to the 8 on-board LEDs, all the 8 LEDs would seem to be on simultaneously! We need a slow clock!

- To slow down the input clock, we need a clock divider. We can use the Digital Clock Module (DCM) inside the Spartan-3A family devices, or we can construct our own using a large counter. For now, we will be using the second option. We'll use DCM at a later date.

I used a 27-bit counter, and connected the 8 upper bits (MSBs), ie bits 19-26, to the 8 on-board LEDs of Elbert. This gave me the clock frequency of ~11.44Hz at the lowest(least significant bit) LED!

I used a 27-bit counter, and connected the 8 upper bits (MSBs), ie bits 19-26, to the 8 on-board LEDs of Elbert. This gave me the clock frequency of ~11.44Hz at the lowest(least significant bit) LED!

New VHDL Code for Elbert

8 Bit Music

:Constraints file for this project:

Video of the above code in action through LEDs on Elbert:

Note: I'm still learning FPGA and VHDL. Any discrepancy/error is regretted. And any new knowledge/information is heartily welcomed!